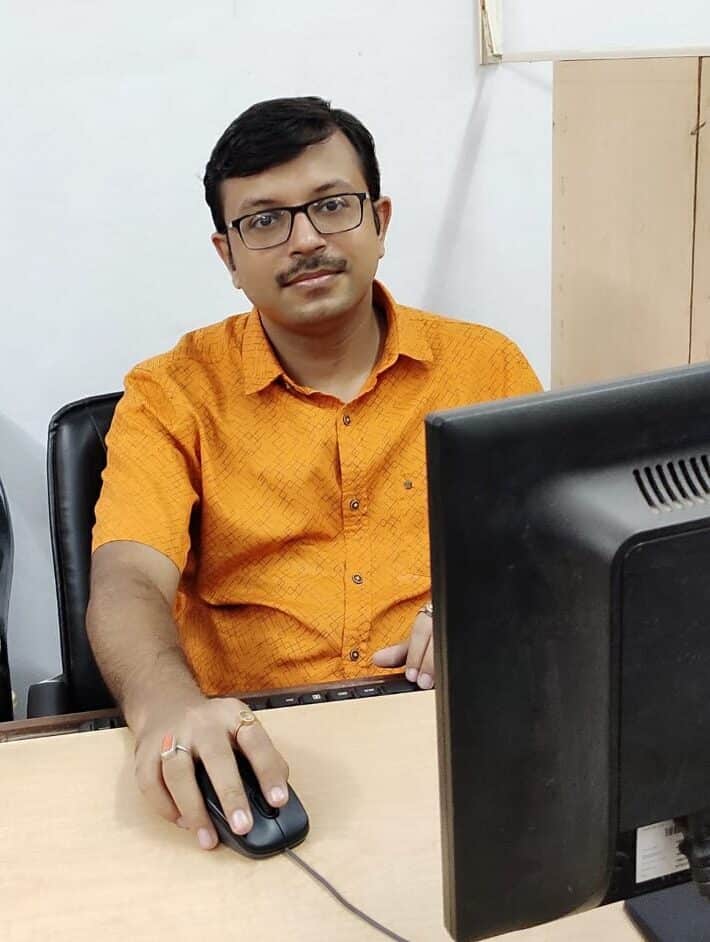

Congratulations Farzan Reza ( Pass out Batch 2024), on receiving an offer for Cloud Support Associate at Amazon, Bangalore with a remuneration of 28LPA.

Congratulations Shabnam Parween (Passout Batch 2024), on receiving offer from FLIPKART with a remuneration of 25.7 LPA

Admissions 2024 - 25

Congratulations Farzan Reza ( Pass out Batch 2024), on receiving an offer for Cloud Support Associate at Amazon, Bangalore with a remuneration of 28LPA

Congratulations Shabnam Parween (Passout Batch 2024), on receiving offer from FLIPKART with a remuneration of 25.7 LPA